A corrida pela inteligência artificial não está sendo decidida apenas nas GPUs. O novo gargalo — silencioso, caro e cada vez mais determinante — encontra-se na memória: na quantidade que pode ser movimentada por segundo, na que pode ser próxima ao processador e na quantidade de energia que é consumida para manter esse fluxo constante de dados. Em 2026, com os centros de dados se expandindo a um ritmo que testa a rede elétrica e as cadeias de fornecimento, o foco se desloca para um componente que durante anos parecia “comoditizado”: a DRAM.

O sintoma é claro. Empresas como a TrendForce elevaram significativamente suas previsões de aumento de preços para a memória convencional, em um mercado tensionado pela demanda de infraestrutura de IA e pela preferência dos grandes fabricantes por destinar capacidade a produtos mais rentáveis, como a HBM (High Bandwidth Memory). Paralelamente, o impacto começa a atingir a eletrônica de consumo: vários fabricantes de PCs estão avaliando, conforme informações publicadas nas últimas horas, alternativas de suprimento na China diante da escassez global.

Nesse contexto, surge um movimento notável: a SoftBank, através de sua subsidiária SAIMEMORY, e a Intel assinaram um acordo de colaboração para avançar na comercialização de uma tecnologia denominada Z-Angle Memory (ZAM), uma memória de nova geração projetada para combinar alta capacidade, alto largura de banda e baixo consumo, com foco em cargas de trabalho de treinamento e inferência de modelos em larga escala.

A aliança foi formalizada em 2 de fevereiro de 2026, e o plano oficial estabelece marcos concretos: protótipos durante o ano fiscal que termina em 31 de março de 2028 e objetivo de comercialização para o ano fiscal de 2029. A SAIMEMORY, criada em dezembro de 2024, liderará o desenvolvimento e o lançamento no mercado, enquanto a Intel proporcionará base tecnológica e suporte à inovação.

A SoftBank enquadra essa aposta dentro de sua estratégia para reforçar infraestrutura vinculada a centros de dados e IA, enfatizando a transição de uma fase de treinamento massivo para a inferência operacional, onde mover grandes volumes de dados para os aceleradores torna-se crítico.

O ZAM se apresenta como uma arquitetura de memória que busca aumentar sua capacidade e desempenho sem aumentar o tamanho físico. O objetivo, em termos simples, é aproximar mais memória “rápida” dos chips que realizam a computação, reduzindo as fricções típicas: latência, consumo e limitações de embalagem.

Embora o projeto esteja ainda em uma fase inicial, várias análises do setor o posicionam como uma tentativa de superar as limitações atuais da HBM, que tem sido crucial para a IA devido ao seu enorme largura de banda, mas que também impõe compromissos em capacidade e custos. O raciocínio por trás é que o setor necessita de memórias que não obriguem a escolha entre “mais largura de banda” ou “mais capacidade”.

O coração tecnológico do acordo está no trabalho prévio da Intel por meio de sua iniciativa Next Generation DRAM Bonding (NGDB), desenvolvida no âmbito do programa Advanced Memory Technology (AMT) do Departamento de Energia dos EUA. A Sandia, um dos laboratórios nacionais, já apresentou avanços relevantes na proposta, que visa melhorar o desempenho da memória sem comprometer outros fatores críticos.

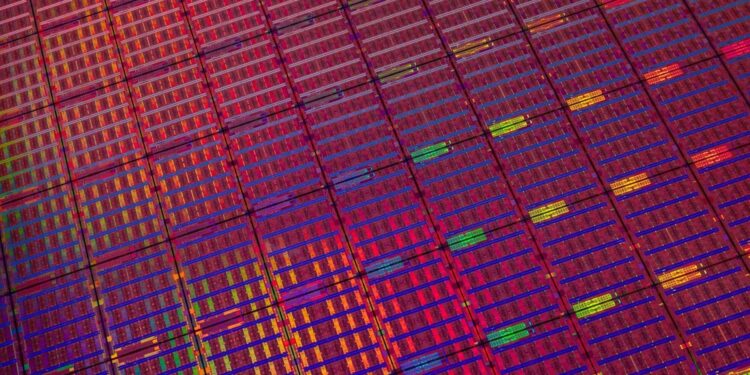

No entanto, mesmo com os avanços, a ZAM ainda é promissora, com cronograma audacioso, mas enfrenta desafios conhecidos na fabricação de semicondutores, como o rendimento por wafer e a complexidade de embalagem. A mensagem é clara: se a IA é uma corrida de infraestrutura, a memória se torna o setor onde tropeços são mais fáceis de ocorrer, gerando oportunidades para arquiteturas novas e colaborações inesperadas.